Si5351Aは Multisynth の delay パラメータを使って直交信号を出力することができるが,パラメータの設定範囲が最大127のため,直交信号を出力できる範囲はおよそ3MHz以上に限られる.(Si5351で直交信号) そこで 別の方法によって 3MHz以下の直交信号を得ることにした.

Si5351の構成は図通りで,Mutisynthの分周比M0, M1をある値で固定しておき,PLLのフィードバック分周比Nを変化させて周波数をコントロールするのが一般的.

今回のポイントは,M0, M1も分数分周比をとることができるので,M0, M1によって周波数を細かく制御することが可能という点.ただ,Mの値の制御ではスムーズな周波数制御はできないと思うのでMの制御は位相差π/2を得るためだけの手段とし,周波数の制御はPLLの分周比Nの制御で行う.

Mの制御で希望の位相差を得るには,M0,M1を時間差をつけて変化させればよい.

例えば,M0, M1 = m’ としておいてPLLリセットする(これで位相が0にそろう).

その後, M0 = m (m<m’, M1 = m’ はそのまま) とすれば f I>f Q となり

周波数差 fd = f I – f Q が生じる.

これによって,f I の位相が f Q に対して時間経過とともに進んでいく.

経過時間を Td とすれば,位相の進み θd は次式で表される.

よって,θd = π/2 となる Td は,

![]()

となるので,この時間経過後に M1 = m にセットすれば,π/2の位相差を持った信号が得られる.この操作は一度行えばよい.それ以降,m の変更がなく,かつ,周波数の変更をPLLで行えば位相差は維持される.

例として,2.0MHzの直交信号を得る場合について手順を示す.

条件は,m = 300, fd = 4Hz, Multisynthのモードは fractional.

- fvco = 300*2.0MHz = 600MHz となるよう N = 600MHz/25MHz = 24 にセット

- 出力周波数 f I, fQ = 2.0MHz – 4Hz となるよう,

M0, M1=600MHz / ( 2MHz-4Hz ) = 300.0006 にセット - PLLリセット

- M0 = 300 にセット

- Td = 1/(4fd) = 62.5ms 経過後に M1 = 300 にセット

これで2MHzの直交信号が得られる.以降,周波数を変化させる場合,例えば1.99MHzに変更するには,Nのみ変更し,N = 1.99MHz*300 / 25MHz = 23.88 にセットする.

ここで重要なのはPLLリセットしないこと.

fd は任意だが小さい方が位相差の精度がよいかもしれない.ただしTdが大きくなり待ち時間が長くなる.

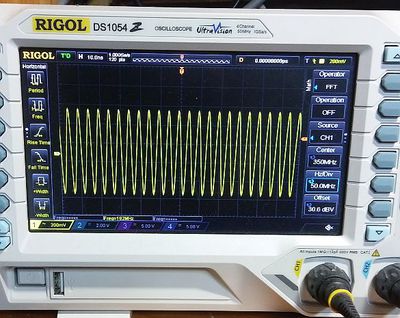

以下動作例

出力周波数=1.18MHz

出力周波数=588kHz

保証された動作ではないかもしれないが,いまのところ変な動作はしていない様子.