直交信号が得られると非常に有用なので,Si5351で試してみた.

MultiSynth のDelay機能を使えば,ch間の位相差(時間差)を設定できる.

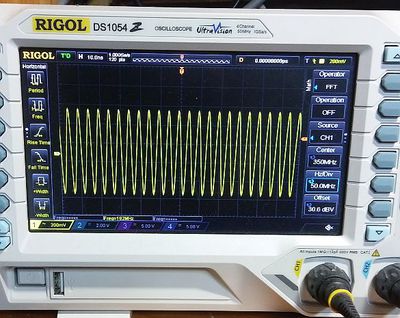

結論としては,3MHz以上で直交信号を得ることができた.

サンプルコード(Si5351Aの設定に関する部分のみ)を修正しておいた.

ch0, ch1 に出力されるようになっている.

以下詳細.

Delayは,td= N/(4*fvco) —-(1)

で,N は,0~127の範囲で設定できる.

出力周波数は, fout=fvco/(M*R) —- (2)

(M:MultiSynthの分周比,R:出力dividerの分周比)

90度位相差に相当するDelayは, td=1/(4*fout) —- (3)

(1), (2), (3) より,

N=M*R

つまり,fvco と fout の比(fvco/fout )を設定すれば

90度の位相差となる.

ここでNの値として設定できるのが最大127まで,というのが制限になる.

fvcoの下限は375MHzであるから,

(fvco=fxtal*(a+b/c) で,a>=15, fxtal=25MHz.よって25*15=375 )

375/127≒2.95MHz.これが,直交信号が得られる下限となる.

ちなみに,VCO自体の周波数範囲は,

使用したチップの実測で 200MHz~1160MHz くらいあるようで,

意外と広帯域である.

3MHz

7MHz

14MHz

21MHz

28MHz

50MHz